system verilog - What is SystemVerilog equivalent for VHDL fixed_pkg and float_pkg? - Electrical Engineering Stack Exchange

SystemVerilog Design: User Experience Defines Multi-Tool, Multi-Vendor Language Working Set Ways Design Engineers Can Benefit fr

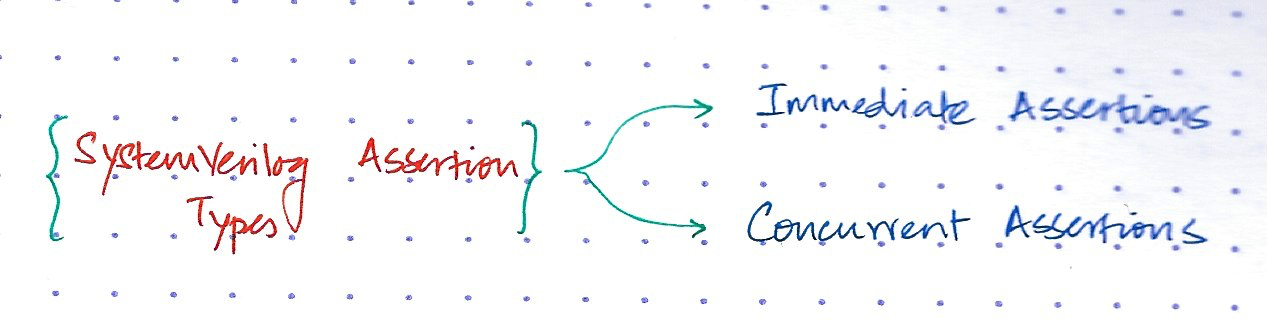

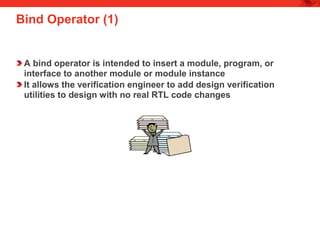

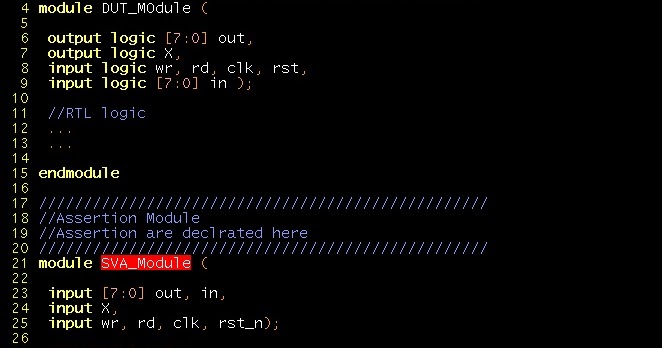

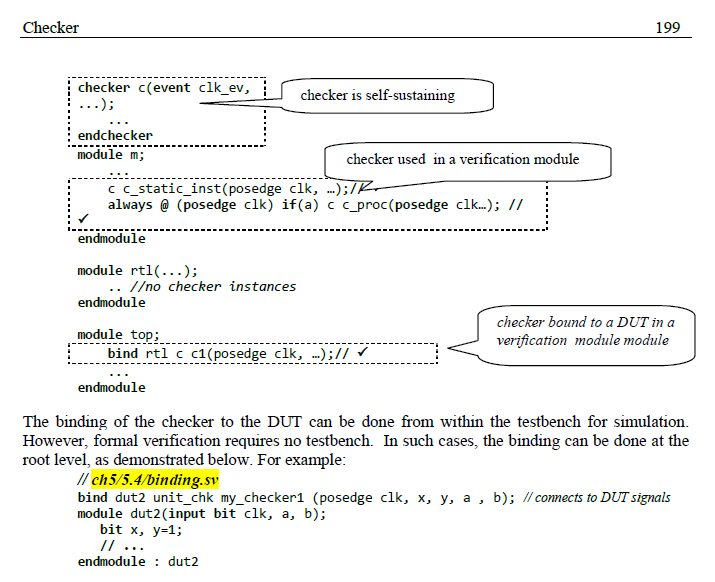

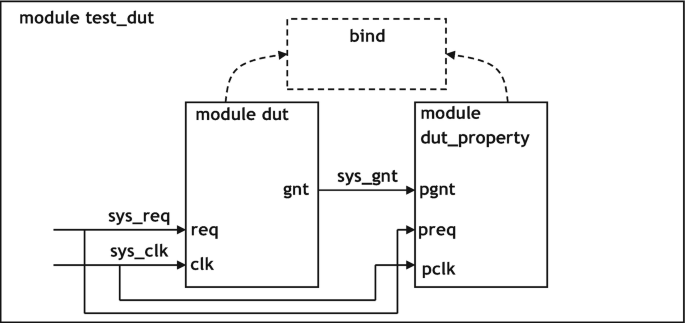

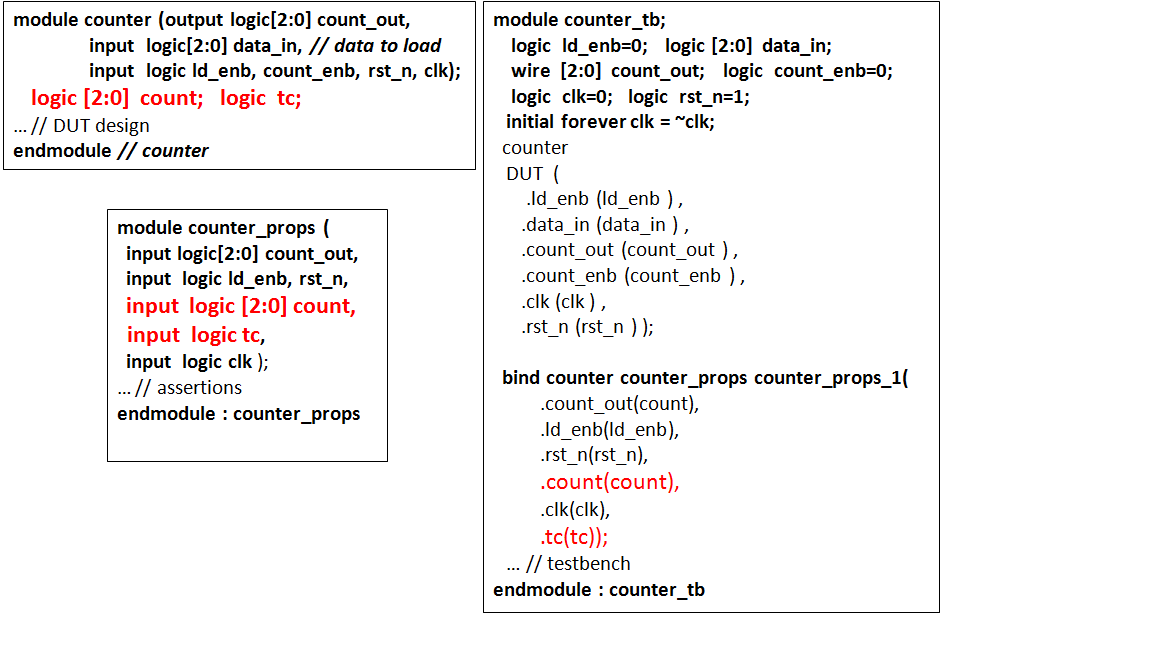

SystemVerilog Assertions Design Tricks & SVA Bind Files | Assertion-Based Verification for FPGA and IC Design | Verification Academy